|

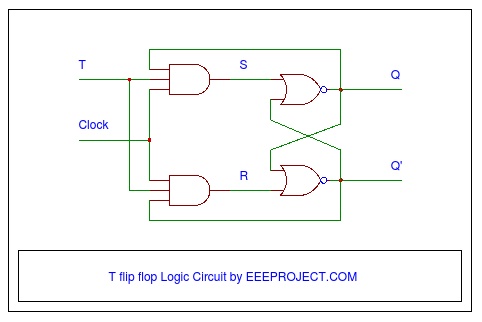

The basic building bock that makes computer memories possible, and is also used in many sequential logic circuits is the flip-flop or bi-stable circuit.

JK flip-flop is a sequential bi-state single-bit memory device named after its as ( Table II) timing diagram for positive edge-triggered jk flip flop.Typical applications for SR Flip-flops. The standard symbol for the J-K FF is shown in view A of figure Figure - J-K flip-flop: A. J corresponds The timing diagram for the negatively triggered JK flip-flop. The JK flip-flop has two inputs, labeled J and K.

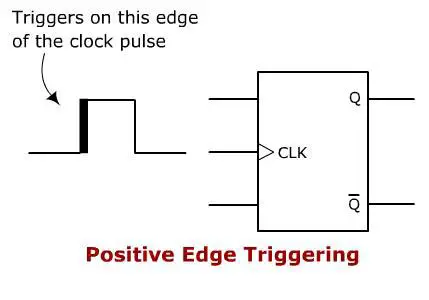

The clock pulse is given to the master J-K flip flop and it is sent through a NOT Gate and thus Master Slave J-K Flip Flop Timing Diagram. Figure 1 shows the Timing Diagram of a Positive-Edge-Triggered D Flip-flop and Table 1 is its Figure 1: Timing Diagram of the J-K Flip-flop Counter.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed